## **ADVANCED COMPUTING**

**JSR-94-130**

#### **DECEMBER 1996**

**The Mitre Corporation JASON Program Office 1820 Dolley Madison Blvd** McLean, VA 22102-3481 (703) 883-6997

| REPORT DOCUMENTATION PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                      |                          |          |                    | Τ                      | Form Approved<br>OMB No. 0704-0188          |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------|----------|--------------------|------------------------|---------------------------------------------|--|--|

| Public reporting burden for this collection of information estimated to average 1 hour per response, including the time for review instructions, searc hing existing data sources<br>gethering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this<br>collection of information, including suggestions for reducing this burden, to Washington Headquarters Services, Directorate for information Operations and Reports, 1215 Jeffered<br>Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget. Paperwork Reduction Project (0704-0188), Washington, DC 20503. |                                                      |                          |          |                    |                        |                                             |  |  |

| 1. AGENCY USE ONLY (Leave bi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | unk) :                                               | December 199             | 6        | 3. REPORT TYPE A   | ND DA                  | TES COVERED                                 |  |  |

| 4. TITLE AND SUBTITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | L                                                    |                          | <u> </u> | L                  | 5. FU                  | INDING NUMBERS                              |  |  |

| Advanced Computing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                      |                          |          |                    |                        |                                             |  |  |

| 6. AUTHOR(S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |                          |          |                    |                        | 13-958534-04                                |  |  |

| W. Dally, A. Despain,<br>P. Weinberg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                      |                          | D. Nelso | n, W. Press,       |                        |                                             |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES)   |                          |          |                    |                        |                                             |  |  |

| The MITRE Corporation<br>JASON Program Office                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                      |                          |          |                    |                        | EPORT NUMBER                                |  |  |

| 1820 Dolley Madison Blvd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                      |                          |          |                    |                        | JSR-94-130                                  |  |  |

| McLean, Virginia 221                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 02                                                   |                          |          |                    |                        |                                             |  |  |

| 9. SPONSORING/MONITORING AGENCY NAME(S) AND ADDRESS(ES)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                      |                          |          |                    |                        | PONSORING/MONITORING<br>GENCY REPORT NUMBER |  |  |

| Advanced Research P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                      | gency                    |          |                    | 1                      |                                             |  |  |

| 3701 North Fairfax Drive<br>Arlington, Va. 22203-1714                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                      |                          |          |                    |                        | JSR-94-130                                  |  |  |

| 11. SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                      |                          |          |                    | ļ                      | · · · · · · · · · · · · · · · · · · ·       |  |  |

| 11. SUPPLEMENTARY NUTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                      |                          |          |                    |                        |                                             |  |  |

| 12a. DISTRIBUTION/AVAILABILIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Y STATEME                                            | NT                       |          |                    | 125.                   | DISTRIBUTION CODE                           |  |  |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                      | •••••                    | •••      |                    |                        |                                             |  |  |

| Approved for public                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Approved for public release; distribution unlimited. |                          |          | Dis                | stribution Statement A |                                             |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                      |                          |          |                    |                        |                                             |  |  |

| 13. ABSTRACT (Maximum 200 word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | is)                                                  |                          |          |                    |                        |                                             |  |  |

| The task of the study to construction of advance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                      |                          |          |                    | the d                  | lesign and                                  |  |  |

| Focus was on two topic<br>architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | cs: super                                            | conducting and           | single   | electron" logi     | c, and                 | advanced                                    |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                      |                          |          |                    |                        |                                             |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                      |                          |          |                    |                        |                                             |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                      |                          |          |                    |                        |                                             |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                      |                          |          |                    |                        |                                             |  |  |

| 14. SUBJECT TERMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                      |                          |          |                    | H                      | IS. NUMBER OF PAGES                         |  |  |

| single electron, advan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ced archi                                            | tecture                  |          |                    |                        |                                             |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                      |                          |          |                    | 1                      | 16. PRICE CODE                              |  |  |

| 17. SECURITY CLASSIFICATION<br>OF REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18. SECURIT                                          | Y CLASSIFICATION<br>PAGE |          | ITY CLASSIFICATION |                        | 0. LIMITATION OF ABSTRACT                   |  |  |

| Unclassified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      | ssified                  | 1        | classified         |                        | SAR                                         |  |  |

| NSN 7540-01-280-5500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                      | •                        |          | <u></u>            |                        | Standard Form 298 (Rev. 2-89)               |  |  |

1

Preseribed by ANEI Std. 238-18 298-102 -----

## **Table of Contents**

| <u>Section</u>                                      | <u>Page</u> |

|-----------------------------------------------------|-------------|

| Introduction                                        | 1           |

| Superconducting and Single Electronics              | 13          |

| Conclusions: Superconducting and Single Electronics | 47          |

| Advanced Architecture                               | 51          |

| Conclusions: Advanced Architecture                  | 94          |

Advanced Computing

iii

This page left blank intentionally

ţ.

.

#### Introduction

La desta de la contra de la contr

# Introduction

This briefing was presented by Bob Westervelt and Bill Dally; other JASONs who contributed to the project are listed.

The task of the study was to examine technical issues associated with the design and construction of advanced computers on a twenty year time frame. Current CMOS technology was not covered, because it has been examined in detail by other groups and its future development can be predicted reasonably well.

We focused on two topics: superconducting and "single electron" logic, and advanced architecture. The first half of this brief, presented by Bob Westervelt, describes single flux quantum and single electron logic; the second half, presented by Bill Dally, discusses architecture issues.

# Task

To examine technical issues associated with the design and possible future production of computers in the next century. What lies beyond (or to the side of) CMOS?

# Workshops

#### Superconducting and Single Electronics Workshop

Mac Beasley John Clarke Jim Kaschmitter Marc Kastner Mark Ketchen Dick Harris Kostya Likharev John Martinis Donald Miller Hans Mooij Arnold Silver Ted Van Duzer Stu Wolf Stanford/ARPA DSRC U.C. Berkeley Consultant M.I.T. I.B.M. NIST Boulder SUNY Stony Brook NIST Boulder Westinghouse Delft TRW U.C. Berkeley ARPA/NRL

#### Advanced Architecture Workshop

John Hennessy Peter Kogge Steve Oberlin Greg Papadopoulos Burton Smith Stanford/Silicon Graphics IBM/Loral/Notre Dame Cray Research MIT/Thinking Machines Tera Computer

### Workshops

Two workshops were held during the summer study in La Jolla, one on superconducting and single electronics, and one on advanced architecture. A number of distinguished researchers from academia and industry, listed above, either attended the workshops, or were consulted separately.

# Outline

| <ul> <li>Introduction</li> </ul>                                                                                                         | R. Westervelt      |

|------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| <ul> <li>Computer hardware - past, present, future</li> </ul>                                                                            |                    |

| <ul> <li>Single Electronics         <ul> <li>Single flux quantum devices</li> <li>Single electronic devices</li> </ul> </li> </ul>       | R. Westervelt      |

| <ul> <li>Advanced Computer Architecture         <ul> <li>Massive parallelism</li> <li>Importance of Communication</li> </ul> </li> </ul> | W. Dally           |

| <ul> <li>Conclusions and Recommendations</li> </ul>                                                                                      |                    |

|                                                                                                                                          | Advanced Computing |

## Outline

The briefing consisted of three parts, an introduction to general issues concerning computer hardware in the past, present, and future, presented by Bob Westervelt, a description of two possible future technologies - single flux quantum logic and single electron logic - by Bob Westervelt, and a discussion of advanced computer architecture, presented by Bill Dally and written up separately.

# SIA Roadmap for CMOS Technology

| Year                                              | <u>1995</u> | <u>1998</u> | <u>2001</u> | <u>2004</u> | <u>2007</u> |

|---------------------------------------------------|-------------|-------------|-------------|-------------|-------------|

| Feature size (microns)                            | 0.35        | 0.25        | 0.18        | 0.12        | 0.1         |

| Gates/chip                                        | 800k        | 2M          | 5M          | 10M         | 20M         |

| Bits/chip DRAM                                    | 64M         | 265M        | 1G          | 4G          | 16G         |

| Bits/chip SRAM                                    | 16M         | 64M         | 256M        | 1G          | 4G          |

| Chip size (mm <sup>2</sup> ) Logic/microprocessor | 400         | 600         | 800         | 1000        | 1250        |

| Chip size (mm²) DRAM                              | 200         | 320         | 500         | 700         | 1000        |

| Wafer diameter (mm)                               | 200         | 200-400     | 200-400     | 200-400     | 200-400     |

| Interconnect levels (logic)                       | 4-5         | 5           | 5-6         | 6           | 6-7         |

| Max power (W/die) High Performance                | 15          | 30          | 40          | 40-120      | 40-200      |

| Power supply (V) (Portable)                       | 2.2         | 2.2         | 1.5         | 1.5         | 1.5         |

| Number of I/Os                                    | 750         | 1500        | 2000        | 3500        | 5000        |

| Performance (MHz) Off-chip                        | 100         | 175         | 250         | 350         | 500         |

| Performance (MHz) On-chip                         | 200         | 350         | 500         | 700         | 1000        |

## SIA Road Map for CMOS Technology

Representatives from the Semiconductor Industry Association (SIA) have met to consider the future of CMOS technology. This table summarizes their predictions up to the year 2007. These predictions are considered to be reasonably conservative, and the consensus is that the predicted level of performance will probably be achieved.

We use this chart to illustrate a number of points, dealt with in detail later by Bill Dally:

• Driven primarily by the reduction of feature size, the number of gates per chip will increase dramatically by 2007; for example, the DRAM size will increase by a factor of one thousand to 16 Gbits per chip. The predicted increase in clock speed is much smaller, only a factor of five to 1 GHz, on chip.

• The explosion in memory size combined with a moderate increase in clock speed mean that massive parallelism will be required to utilize the memory and obtain a large increase in computational power. Massive parallelism presents challenges both for computer architecture (particularly communication) and for parallel software (efficient use of many processors).

• The chip area devoted to each processor will shrink with the reduction in feature size, so that memory will consume most of the available chip area. This is already true today, but processors and memory are located on separate chips made on separate fabrication lines, and processors are priced much higher. In the future, processors and memory are likely to be found on the same chip made in the same line in order to take advantage of high speed communication on chip. Memory will dominate the chip area and cost, while processors will be relatively inexpensive.

# Performance and Predictions in the 1970's

- Microprocessors in their infancy

- Cray 1 supercomputer (late 1970's)

- ECL bipolar logic circuits

- 100k chips x 4 gates/chip = 400k gates

- 256 MByte SRAM memory (maximum)

- 80 MHz clock speed

- Mainstream predictions for the 1990's (all incorrect)

- High end computers will use bipolar logic.

- Mainframes will dominate micro's.

- CMOS logic is special purpose only low power, slow.

- 1  $\mu$ m linewidth is a fundamental limit.

- Caution is advised!

- Support a range of alternative technologies.

# Performance and Predictions in the 1970's

When attempting to predict what will happen twenty years in the future, it is useful to look twenty years in the past.

In the 1970's microprocessors were in their infancy, and microprocessor based computers had very limited capabilities.

The Cray 1 supercomputer, marketed in the late 1970's, used emitter coupled logic (ECL) and bipolar transistor technology, had about 100,000 chips with about 4 gates per chip, could address a maximum of 256 MBytes of SRAM memory, and ran at a clock speed of 80 MHz. This level of performance has now been surpassed by microprocessor-based systems.

Many mainstream predictions made twenty years ago for computers in the 1990's turned out to be incorrect. What seemed like conservative good sense then, looks less good now. For example:

• High end computers will use bipolar transistors, because they are faster than FET's. The importance of heat production in densely packed integrated circuits was underestimated.

• Mainframes will dominate microcomputers. It was felt that the dominant market would be large business and government users, and that the value of the installed software base would provide the inertia to keep mainframes on top.

• CMOS logic is special purpose only - low power and slow. CMOS was slow with 5  $\mu$ m design rules used in the 1970's, and required special operating voltages. The importance of compactness and low power as fundamental attributes were under appreciated, as well as the speed which could be attained.

### Performance and Predictions in the 1970's (concluded)

• One micron feature size is a fundamental limit. This sounds reasonable given the 0.5  $\mu$ m wavelength of light, but has not held up. Nonlinear resists and advanced processing permit 0.5  $\mu$ m features now, and 0.1  $\mu$ m features are predicted in the year 2007 according to the SIA roadmap.

Caution is advised! Twenty years is a long time over which to predict the future, particularly in a field as active as computers. It is clear that CMOS technology will continue to be important and viable in the future, and will attract major industrial investment. However, it is less clear that CMOS will still be dominant twenty years from now, particularly given the high projected cost of fabrication lines. Revolutions in performance are likely to come through new advances in processing, driven in part by these high costs.

Given the uncertainties, a sensible approach is to invest in a range of exploratory research.

# Superconducting and Single Electronics

### **Single Electronics**

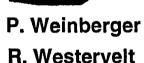

To illustrate possible directions that computer hardware may take in the future, we describe two new technologies in which each bit is represented by a single quantum - single flux quantum logic and single electron logic. Single flux quantum logic could have applications in the near future, because it is based on current superconducting device fabrication technology. Applications of single electron logic probably lie in the future, because very small feature sizes are required for operation at reasonable temperatures.

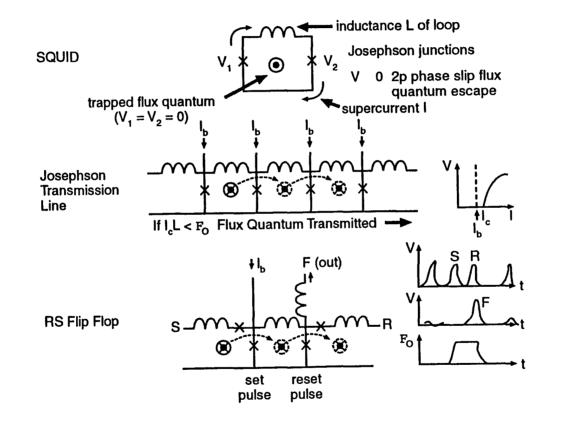

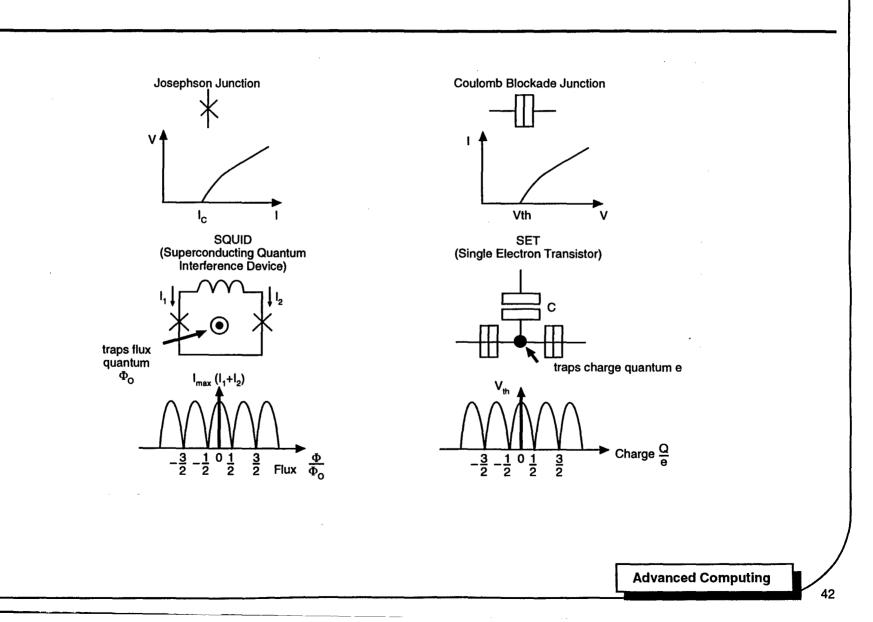

Single flux quantum logic is based on the manipulation of single magnetic flux quanta. The figure at left illustrates a superconducting metal loop with two Josephson tunnel junctions represented by crosses. This is a very useful configuration called a SQUID (superconducting quantum interference device). In a stationary state, a superconducting current I circles the loop. In order for the superconducting order parameter to be single valued, the magnetic flux  $\Phi$  linked by the loop must be equal to a constant plus an integral number of flux quanta  $\Phi_0$ :

$$\Phi_o = \frac{h}{2e}$$

where 2e is the charge of a Cooper pair. Thus the SQUID traps an integral number of flux quanta. Flux quanta can enter and leave the loop by passing through the Josephson junctions. Whenever this happens, the phase of the superconducting order parameter jumps by  $2\pi$ , and a voltage pulse is generated across the junction. We consider this process in detail shortly, and describe how it can be used to construct logic circuits.

Single electron logic is based on the trapping and manipulation of single electrons. The figure on the right illustrates a very small metal island or dot, linked by tunnel junctions to two separate metal contacts. For micron sized and larger dots the electrostatic energy of a single electron on the dot is negligible. However, for submicron dots, the Coulomb charging energy e<sup>2</sup>/2C can become significant.

#### Single Electronics (concluded)

If e<sup>2</sup>/2C is larger than the thermal energy kT, and the tunneling resistance of each contact is greater than h/e<sup>2</sup>, the number of electrons on the dot becomes well-defined, and the quantization of electronic charge leads to the requirement that the total charge Q on the dot be an integral multiple of e. Electrons pass onto and off of the dot by tunneling to one of the metal contacts, generating a current pulse. We describe below how these physical processes can be used to construct memory elements. In the following presentation, we treat single flux quantum logic first, then describe single electron logic.

This page intentionally left blank.

.

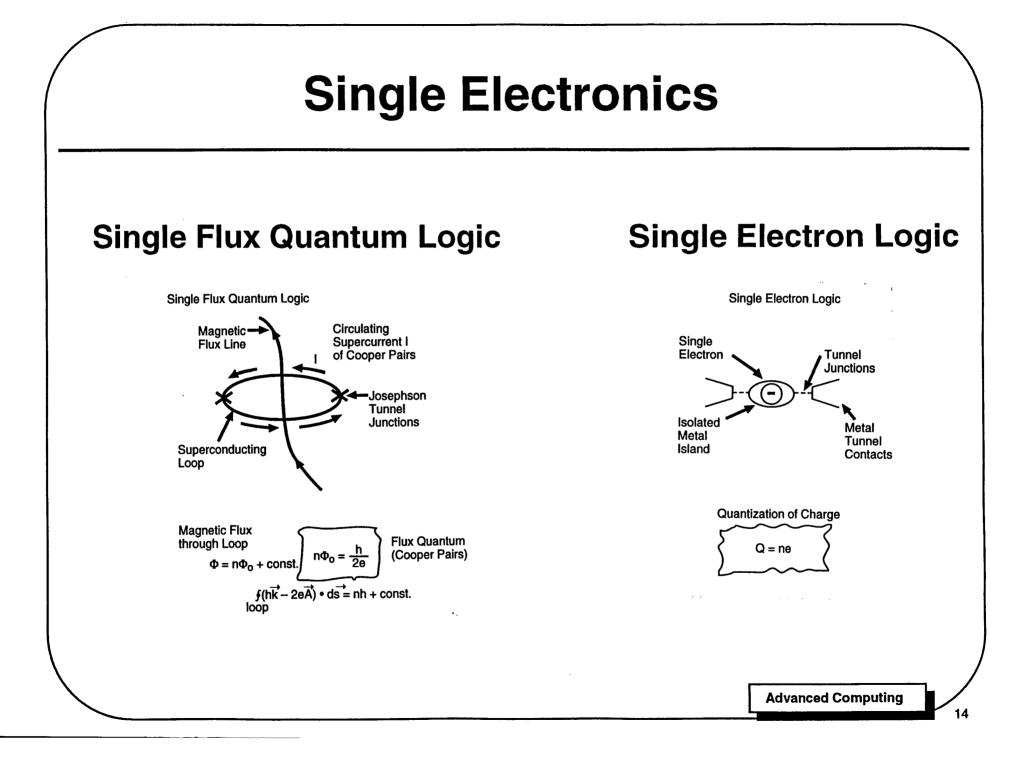

### **RCSJ Model**

In order to understand the operation of single flux quantum logic, we need first to understand Josephson junctions. The RCSJ (resistively and capacitively shunted junction) model of Josephson junctions represents an actual device by a parallel combination of an ideal junction with a capacitance *C* and resistance *R*. This model describes the operation of experimental devices very well. The equations of motion for the RCSJ model are given to the right of its circuit diagram: the total current I is the sum of capacitive and resistive contributions with the Josephson current *I*<sub>c</sub> sin  $\theta$ , where *I*<sub>c</sub> is the critical current of the junction beyond which it develops voltage, and  $\theta$  is the difference of the phase of the superconducting order parameter across the junction. The voltage *V* is given by the second Josephson equation  $V=(h/2e)d\theta/dt$ . These two first order differential equations can be combined into one second-order differential equation for the phase difference  $\theta(t)$ , as shown.

It is an interesting and very useful fact that the equation of motion for the phase  $\theta(t)$  in the RCSJ model is exactly the same as the equation of motion for the position x(t) of a ball of mass *m* moving in a tilted sinusoidal washboard potential *U* with viscous damping  $\gamma$ . As shown, the mass m is proportional to *C*, and the damping  $\gamma$  is proportional to 1/R. The tilt of the washboard potential is proportional to the current I in the RCSJ model, and the velocity is proportional to the voltage *V*.

Using the tilted washboard representation, we can understand the origin of the measured current voltage characteristics of actual Josephson junctions. The overdamped case (small *R*) is most relevant to the present discussion. Suppose that the slope of the washboard potential is initially small, and the ball is at rest in one of the potential minima as shown. As indicated on the schematic current voltage characteristic, this situation applies to currents  $I < I_c$ , for which the voltage is zero. The ball is trapped until the slope added to the washboard potential destroys the local minimum, and the ball starts rolling.

Advanced Computing

19

# (concluded)

As indicated this occurs above  $I = I_c$ , for which the voltage V > 0. For the overdamped case the ball loses enough energy through each cycle of the potential that it is retrapped immediately if the applied slope falls below the critical value. Thus the voltage V across an overdamped junction rapidly switches on and off as the applied current passes above or below  $I_c$ , and the maximum switching rate is  $1/t \sim I_c/2e$  both on and off. At low temperatures one can show that the maximum switching rate for overdamped junctions is essentially limited by the superconducting energy gap  $\Delta$ , corresponding to THz frequencies for practical superconductors. Overdamped junctions have the additional virtue that they are relatively simple and robust, and can be fabricated by a wide range of techniques.

Underdamped junctions used in many previous families of superconducting logic circuits have hysteretic current voltage characteristics, and more complex behavior. For the underdamped case, the ball representing the phase does not lose enough energy in one cycle of the periodic washboard potential to be retrapped. Thus the motion representing voltage can continue even if the slope is reduced somewhat below the critical value, resulting in a hysteretic current-voltage characteristic. This hysteresis is a useful type of switching behavior, but hysteretic junctions suffer the serious disadvantage that the retrapping time is typically many times longer than the detrapping time. Fast logic using hysteretic junctions requires an ac supply which forcibly turns the junctions off.

This page intentionally left blank.

# Rapid Single Flux Quantum (RSFQ) Logic

# Rapid Single Flux Quantum (RSFQ) Logic

Rapid single flux quantum logic is a superconducting logic family developed by Likharev and co-workers at Moscow State University in the late 1980's. It is based on the trapping of single magnetic flux quanta by SQUID's, and their manipulation using pulses of voltage and current. The family is based on non-hysteretic junctions with fast turn on and turn off, the origin of "rapid".

In order to understand the basic principle of operation, consider the SQUID shown, which consists of a loop of superconductor of inductance *L* with two Josephson junctions, indicated by crosses in the circuit diagram. In a stationary state, the phase  $\theta$  of the superconducting order parameter is time independent throughout the circuit, the voltages across both junctions are zero, and a supercurrent *I* circulates around the loop. Under these circumstances the flux  $\Phi = IL$  is time independent and equal to a constant plus an integral number of flux quanta  $\Phi_0$ ; for convenience we will assume that the constant is zero. A current or voltage pulse applied to the right junction which causes a phase slip of  $2\pi$  radians (tilts the washboard potential so that the ball rolls forward one cycle) will cause a flux quantum present in the SQUID to leave to the right. The integral of the voltage pulse across the junction for this process is  $\int dtV(t)=\Phi_0$ .

Next consider a chain of SQUID's connected to each other as shown. Bias currents  $I_b$  are applied to each Josephson junction to bring its current near the critical current, as indicated in the inset, and permit switching by an additional current smaller than  $I_c$ . If the inductance and critical current of each SQUID are sufficiently large that  $I_c L > \Phi_o$ , then a flux quantum can be trapped in each loop of the circuit as described above. Additional current pulses applied to the bias lines will move the flux quantum through the circuit as described above. However, if  $I_c L < \Phi_o$ , then the quantum cannot be trapped permanently in any one loop, because sufficient current cannot be carried without generating a phase slip in one of the junctions. Under these circumstances, the chain forms a Josephson transmission line which passes flux quanta down the line automatically as shown.

# Rapid Single Flux Quantum (RSFQ) Logic (concluded)

Power gain can be achieved in a Josephson transmission line by decreasing the loop inductance *L* along the line while increasing the critical current  $I_c$  to keep the product  $I_cL \sim \Phi_o$  fixed. For this arrangement the energy of a flux quantum in each loop  $\Phi_o^2/2L$  increases along the chain. The energy gain going from one loop to the next, is limited to a modest value in practice by the need to set the bias current in the next loop correctly. Large energy gains can be achieved using a chain with many loops.

An RS flip flop in the RSFQ family is shown at the bottom of the page. It consists of a SQUID with two junctions; the one closest to the set line is bias near the critical current, while the junction near the reset line is unbiased. The two junctions in the set and reset lines are for isolation. Assume that the SQUID is initially empty. A voltage pulse on the set line switches the left junction and moves a flux quantum into the SQUID as shown. When present, the flux quantum creates a circulating supercurrent which biases the right junction of the SQUID part way toward the critical current. A reset pulse which follows a set pulse thus creates a phase slip and corresponding voltage pulse on the output line F, as shown, and moves the flux quantum out of the SQUID to the right. If no set pulse precedes the reset pulse, the right junction is not biased and no switching or output occurs.

Josephson junction logic is capable of switching times in the psec range. Clock synchronization across a logic chip at these speeds is exceedingly difficult, due to delays associated with the speed of light. In order to overcome this problem, RSFQ logic proposes to use a form of self-timed logic, in which a clock pulse is passed from one gate to the next with the signal. The logical state, 1 or 0, is indicated by the presence or absence of a switching pulse between two clock pulses, as illustrated above for the RS flip flop.

This page intentionally left blank.

# Rapid Single Flux Quantum Logic Pro/Con

<u>Pro</u>

works with current processing technology and linewidths

very fast switching both on and off ~ 2p sec demo in ring oscillator <u>Con</u>

low temperatures required 1994 ~ 4K 2010 ~ 80K and above??

low power

propagation

$(> 1 \ \mu m)$

clock synchronization difficult requires self-timed logic modules

drives superconducting propagation delay limits speed benefit transmission lines; dissipation free

superconducting memory not competitive

low spatial density

#### Rapid Single Flux Quantum Logic Pro/Con

#### Pro-

The switching speed of RSFQ logic, both on and off, is extremely fast (~ 2 psec demonstrated in a ring oscillator) and can approach the fundamental limit set by the superconducting energy gap  $\Delta$ . Ultimately RSFQ processors could run 100 to 1000 times faster than their CMOS counterparts. This speed advantage could be important for signal processing applications which must run in near real time, for example digital radar, and could undo the need for massive parallelism.

RSFQ logic is inherently low power, because it does not drop voltage and dissipate power in the quiescent state.

Superconducting transmission lines can transmit high speed pulses without dissipation or serious distortion. Because communication with memory will be very important, this property is highly desirable. RSFQ logic is naturally impedance matched to superconducting lines. Superconducting lines made from high  $T_c$  materials could also be important for semiconductor computers operating at 77K.

RSFQ logic can be constructed using current linewidths (> 1µm) and design rules, so its application need not lie far in the future. Development projects are underway at the superconducting foundries operated by TRW and Hypres in collaboration with Likharev and coworkers at SUNY Stony Brook, and others.

#### Rapid Single Flux Quantum Logic Pro/Con (concluded)

#### <u>Con</u> -

Low temperatures are required for RSFQ logic. Using the present Niobium technology, liquid He temperatures (T ~ 4K) are necessary. The computer must be accompanied by a cooler which adds to the size and expense, and limits the application of this technology to high end systems. Suitable closed cycle coolers are currently available for use with cryopumps. In the future, higher temperature operation may become possible if reliable, mass produced, high  $T_c$  SQUID's are developed.

High speed operation of RSFQ logic requires the use of self-timed logic or related schemes in order to overcome the synchronization problems associated with propagation delay. A similar problem also occurs for fast CMOS logic at ~ 1 GHz clock speeds. Approaches to self-timed logic (described in the architecture section) have been developed, but require several times the number of gates as conventional logic.

Propagation delay limits the potential speed benefit of RSFQ logic. Even with a single fast processor, the propagation delay to and from memory would pose a serious problem. Similar problems also occur for fast CMOS systems. Their solution requires new approaches to managing the physical location of information in memory and new approaches to managing latency, discussed in the architecture section.

Compatible memory is a problem. Superconducting single flux quantum memory is not competitive because it has relatively low spatial density. The area required to trap a flux quantum is large for moderate critical currents: one needs  $l_c L > \Phi_o$ , the small inductance *L* associated with small sizes requires greater  $l_c$ . Fast memory access is also a problem, and will probably require paging from a larger slower memory to a smaller faster one.

This page intentionally left blank.

## **Coulomb Blockade**

#### **Coulomb Blockade**

We now turn to a description of single electron logic. Because very small feature sizes (~ 10 nm) are required for operation near room temperature, the application of this technology probably lies in the future. However, the physical principles of operation are studied today.

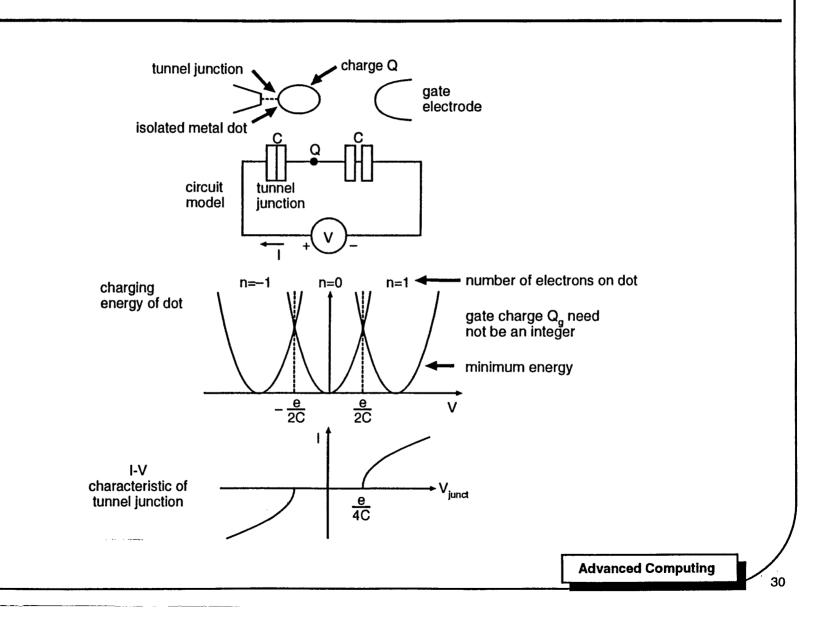

Single electron logic is based on a phenomenon known as the Coulomb blockade. To illustrate this phenomenon we consider a quantum box consisting of an isolated normal metal dot connected to one normal metal contact via a tunnel junction, and to another normal metal contact via capacitive coupling, as shown. For simplicity assume that the capacitance of both the tunnel junction and the capacitive coupling both have the same value *C*, so that the total series capacitance is *C*/2 and the total capacitance of the dot is  $C_{\Sigma} = 2C$ . If the resistance of the tunnel junction is larger than h/e<sup>2</sup>, the number of electrons on the dot is well defined.

A circuit model for the quantum box connected to a voltage source is shown, where we use the double box symbol for the tunnel junction. In the absence of any stray charges, the total charge Q on the dot is an integral number of electronic charges Q = ne. The total electrostatic charging energy U of the dot depends both on the applied voltage V and the dot charge Q:

$$U = \frac{CV^2}{4} + \frac{(ne)^2}{4C} - \frac{neV}{2}$$

Advanced Computing

31

#### Coulomb Blockade (continued)

The first two terms are the electrostatic charging energy of the two capacitors, and the third term is the work done by the voltage source to move the extra charge *-ne*/2 induced by the dot charge *ne* onto the left capacitor. This equation simplifies to:

$$U = \frac{(CV - ne)^2}{4C}$$

Plots of the total charging energy U are shown below the circuit diagram for n = -1, 0, and +1. Electrons will tunnel onto and off of the dot in order to minimize the total charging energy, so that the stationary values of the energy follow the minimum energy as indicated. Thus the dot charge is Q = 0 over the finite range of voltage -e/2C < V < e/2C, the dot charge is Q = e for e/2C < V < 3e/2C, etc.

This effect is known as the Coulomb blockade: the Coulomb charging energy of the dot requires a finite applied voltage to overcome the electrostatic barrier to tunneling of electrons. The current voltage characteristic of the tunnel junction is indicated at the bottom of the figure. Current can only flow through the tunnel junction when the voltage across the junction  $V_{junct}$  provides an energy  $eV_{junct}$  equal to the charging energy  $e^2/4C$ . In the present example, all current flow is transient, associated with charging the dot.

Through the Coulomb blockade, the quantization of electronic charge provides a natural nonlinear threshold element which can be used to construct memory elements and logic circuits. The threshold voltage is given in general by  $V_{\text{th}} = e^2/2C_{\Sigma}$  where  $C_{\Sigma}$  is the total capacitance of the dot.

#### Coulomb Blockade (concluded)

In order to observe the Coulomb blockade, the temperature must be low enough that the thermal energy is small compared with the charging energy:

$kT < e^2/2C_{\Sigma}$ .

To avoid unwanted switching due to thermal activation, kT must be quite small, a factor of 10 to 100 times smaller than the charging energy. Because the charging energy increases as the size of the device is reduced, smaller devices operate at higher temperatures.

One can make a rough estimate of the temperature of operation by using the fact that the capacitance  $C_{\Sigma}$  is typically dominated by the self-capacitance of the dot. The charging energy U<sub>th</sub> is then:

$U_{th} = e^2/2C_{\Sigma} \sim e^2/4\pi\epsilon_o r$

where r is the linear dimension of the dot. For current device sizes r ~ 100 nm,  $U_{th}$  ~ 10 meV (100 K) and the maximum operating temperature is  $T_{op}$  ~ 1 K to 10 K. As devices become smaller, the operating voltage and temperature increase in proportion to 1/r: for r ~ 10 nm,  $U_{th}$  ~ 0.1 eV (1000 K) and the maximum operating temperature is  $T_{op}$  ~ 10 K to 100 K, a more convenient range for applications.

## **Single-Electron Transistor**

### **Single-Electron Transistor**

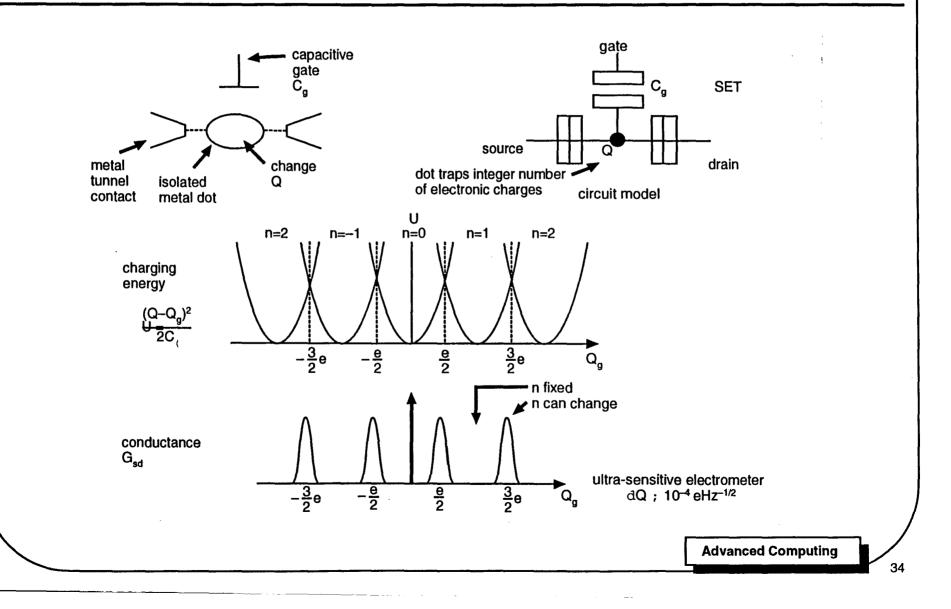

The Coulomb blockade can be used to construct a type of field effect transistor with charge sensitivity much less than a single electron: the so-called single electron transistor (SET). The SET is particularly significant for logic circuits, because it serves to trap and manipulate single electrons, just as the SQUID traps and manipulates single magnetic flux quanta.

A schematic diagram and a circuit model for a single electron transistor are shown at the top of the page. The SET consists of an isolated normal metal dot with tunnel junctions to two normal metal contacts which act a the source and the drain. A third gate electrode is located nearby, completely isolated from the dot except for electrostatic coupling. If the resistance of each tunnel junction is greater than h/e<sup>2</sup>, the number of electrons on the dot is well defined.

Single electron transistors were first made in the late 1980's from metal films using oxide tunnel junctions. SET's have also been made using confined regions of electron gas in semiconductor heterostructures. The basic principles of operation are the same for both types.

The total charging energy U of the dot vs. gate voltage, with the source and drain grounded is given by:

$$U = \frac{\left(ne - Q_g\right)^2}{2C_{\Sigma}}$$

where ne is the total charge on the dot, with n an integer,  $Q_g$  is the charge on the gate capacitor, and  $C_{\Sigma}$  is the total capacitance of the dot to all locations. Note that  $Q_g$  need not be an integral multiple of e, because it is the surface charge induced by polarization of the dot by the gate voltage and can have any value.

#### Single-Electron Transistor (concluded)

The Coulomb blockade in this structure provides the mechanism for a very sensitive field effect transistor. A plot of the charging energy U vs. gate charge is shown for several values of n at the middle of the page, and a plot of the source to drain conductance  $G_{SD}$  vs. gate charge is shown at the bottom. The charging energy U consists of a family of parabolas, one for each value of n. Adjacent parabolas intersect at half integral values of gate charge  $Q_g = [(2n + 1)/2]e$  as shown. Near intersections, the total energy U is comparable for n and n + 1 electrons, and the number of electrons on the dot can change, allowing charge to flow from source to drain. Away from the intersections, the energy U is different numbers of electrons, and the number of electrons is fixed, preventing the flow of current. Thus the source to drain conductance  $G_{SD}$  is peaked at values of gate charge  $Q_g = [(2n + 1)/2]e$  separated by a single electronic charge. This property leads to the name single electron transistor.

Single electron transistors are impedance converters with large power gain, and they make very sensitive electrometers: charge sensitivity  $\delta Q \sim 10^{-4} e / \sqrt{Hz}$  has been achieved at dilution refrigerator temperatures  $T \sim 100$  mK.

This page intentionally left blank.

.

### **Single Electron Memory**

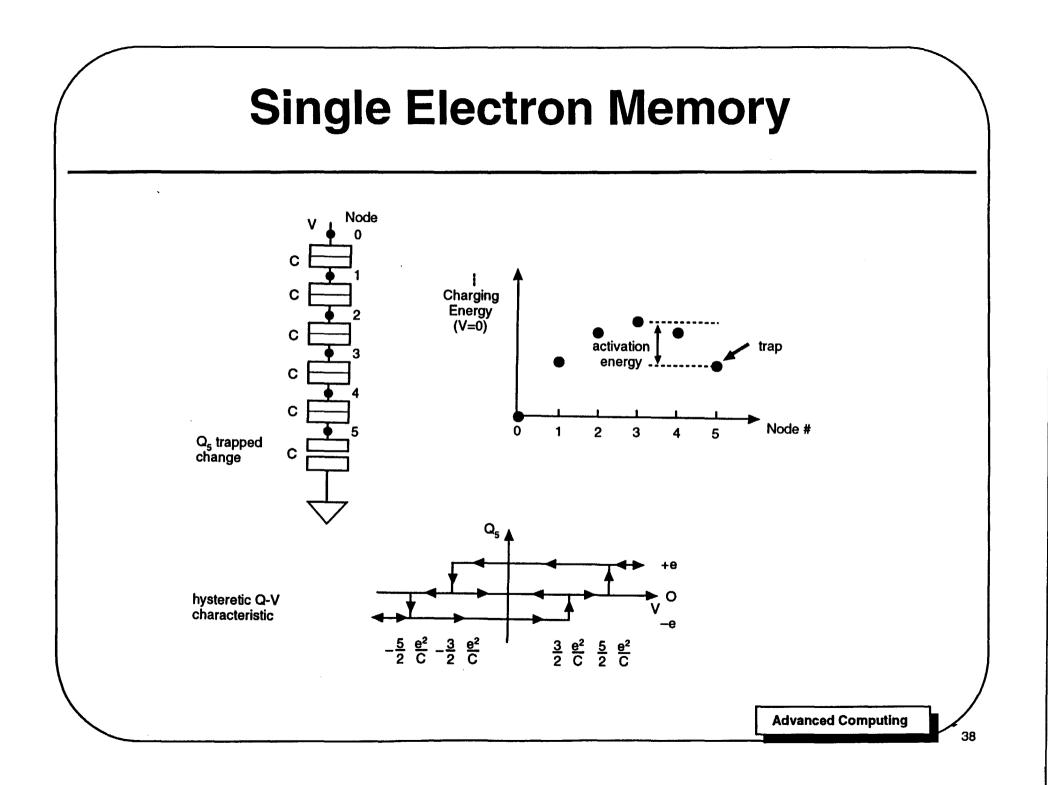

Perhaps the most promising future application for the Coulomb blockade is in single electron memory elements. Dresselhaus et. al. (1994) have demonstrated the operation of a hysteretic Coulomb trap which holds a single electron for times in excess of 2 hours at T = 50 mK. More spectacular results have recently been obtained by workers at Hitachi, who demonstrated a memory element operating at room temperature, based on the single electron principles. The Hitachi device uses a processing trick to achieve very small sizes necessary for room temperature operation - percolating conduction paths in a polysilicon gate. We describe the Stony Brook device below, because its operation is better understood.

The Stony Brook memory element consists of a chain of small normal metal tunnel junctions, as illustrated in the circuit diagram. The chain is broken at one end by a capacitor connected to ground; the other end of the chain is connected to a voltage *V*. For simplicity we assume all of the junctions and the capacitor have the same value of capacitance *C*. Charge can be trapped temporarily on any of the five nodes of the circuit. However, the Coulomb blockade alone is not sufficient to produce a static memory device, because the tunnel junctions leak charge - hysteresis is needed.

One can understand how this chain of junctions traps a single electron by plotting the charging energy  $e^2/2C_{\Sigma}$  necessary to put one electron on a given node of the chain with V = 0. Because the total capacitance to ground  $C_{\Sigma}$  is a minimum at node 3 in the middle of the chain, the charging energy is a maximum at node 3 and decreases to either side, as shown. An electron placed on node 1 will leave through the top tunnel junction, but an electron placed on node 5 is trapped, because the capacitor cannot pass charge. The depth of the trap is the difference between the charging energy on nodes 5 and 3 as indicated; this activation energy can be increased by using a larger capacitor from node 5 to ground.

#### Single Electron Memory (continued)

The trap can be loaded and unloaded by changing the voltage *V*. At the bottom of the page we plot the charge  $Q_5$  on node 5 vs. the applied voltage *V*, as *V* is swept above and below zero. As shown, the trapped charge  $Q_5$  at V = 0 depends on the previous history of V, and can have values -e, 0, or +e for the range of voltage indicated. Assume  $Q_5$  and *V* are initially zero. As *V* is swept positive, the parabola of charging energy vs. node number is tilted downward at the right, and the energy barrier between nodes 1 and 0 decreases, reaching zero at  $V = 5e^{2/2}C$ . At this point a single electron tunnels onto node 1, and rapidly passes through the chain to nodes at lower energy, finally being trapped on node 5. Once trapped, the electron reduces the potential between nodes 0 and 5, preventing additional electrons from entering the chain. As *V* is swept downward through zero, the electron remains trapped until the energy barrier between nodes 4 and 5 is reduced to zero at  $V = -3e^{2/2}C$ . At this point the electron the electron leaves and  $Q_5$  returns to zero. Thus the charge vs. voltage curve has a broad and well defined hysteretic region inside which the presence of a trapped electron can be used to represent the state of the memory element.

The presence of an electron in the trap can be sensed nondestructively by using a single electron transistor as an electrometer, or sensed destructively by measuring the presence of a charge pulse as V is swept negative.

Dresselhaus et. al. (1994) have shown experimentally that a trap constructed from seven junctions with  $R \sim 300 \text{ k}\Omega$  and  $C \sim 0.15 \text{ fF}$  holds single electron for more than two hours at T = 50 mK, with a measured activation energy  $\Delta U/k \sim 4K$ . If this level of performance could be achieved at higher temperatures, it would be useful for practical circuits.

#### Single Electron Memory (concluded)

The primary obstacle to the use of single electron memory elements is formidable: the need to construct junctions sufficiently small that the operating temperature is acceptable. In order to achieve operating temperatures ~ 100 K, junctions smaller than 10 nm are probably required. It is this obstacle which puts the projected use of single electron memory far in the future. However, if one develops sufficiently clever processing tricks to make small junctions, as Hitachi may have, this time frame could be much closer.

Additional factors also need to be considered: co-tunneling, parasitic capacitance, and stray charge.

Co-tunneling of the trapped electron through the entire string of junctions at once limits the trapping time. The co-tunneling rate can be reduced to acceptable values by a suitable number of junctions in series.

Parasitic capacitance reduces the barrier to detrapping and thus the operating temperature.

Coupling to stray charge can cause memory upsets. Present junctions are quite sensitive to the motion of stray charge and to electromagnetic pickup and they must be carefully shielded. However, if junctions can be developed which operate at reasonable temperatures ~ 100 K and above, the effects of stray charge will be proportionately less important.

# Duality

## Duality

There is an interesting and powerful duality transformation which relates electrical circuits constructed from Josephson junctions to those made from Coulomb blockade junctions. This duality transformation is an extension of the well known duality transformation for passive electrical circuits which exchanges resistors for conductors and capacitors for inductors.

As illustrated, the current voltage characteristics of a Coulomb blockade junction are very similar to the current voltage characteristics of an overdamped Josephson junction, with the axes reversed. The Coulomb blockade junction passes zero current below a threshold voltage  $V_{th}$ , while the Josephson junction drops zero voltage below the critical current  $I_c$ . Thus the two circuit elements are duals of each other.

Following the rules of the duality transformation in electrical circuit theory, we find that the single electron transistor is the dual of the SQUID: the inductor in the SQUID is transformed into the gate capacitor, and the two Josephson junctions are transformed into two Coulomb blockade junctions. The SQUID traps one quantum of magnetic flux and the SET traps one quantum of electric charge.

This duality extends to the characteristics of the SQUID and SET. The maximum current  $I_{max} = I_1 + I_2$  through the SQUID oscillates periodically with the flux  $\Phi$  in the inductor, as shown, just as the threshold source to drain voltage of the SET for electric conduction oscillates periodically with the gate charge Q.

For every circuit design in RSFQ logic, there exists a dual design in single electron logic with the same equations of motion. For example, the vertical chain of junctions in the single electron memory is similar to the dual of the Josephson junction transmission line in RSFQ logic. This duality is not exploited as much as one might expect, because the dual forms in single electron logic tend to be vertical chains between the power supply rails, a non-standard configuration.

# Single Electron Memory and Logic Pro/Con

<u>Pro</u>

ultimate limit for charge-coupled logic

#### <u>Con</u>

low temperatures required 1990 ~ 1K 2010 ~ 100K?

ultra high packing density ~10<sup>12</sup> bits per 3x3 cm<sup>2</sup> chip

ultra low power

performance improves as size reduced, limited by processing

< 10 nm linewidths needed for ~ 100K operation

high impedance (>100k $\Omega$ ), needs conventional line drivers

stray charge, stray capacitance, and cotunnelling are problems

### Single Electron Memory and Logic Pro/Con

#### <u>Pro</u> -

Single electron logic can be regarded as the ultimate limit of charge coupled logic in which a single electron represents one bit.

Ultra-high packing density could potentially be achieved once the technology to fabricate ultra-small devices is developed. For example, with ~ 10 nm linewidths a 3x3 cm<sup>2</sup> chip could store ~  $10^{12}$  bits of information.

Single electron logic is ultra-low power, because no current is drawn in the quiescent state, and because the energy per bit is very small. For the memory example above, ~ 10 nm linewidths imply an operating voltage  $V_{op} \sim 0.1 V$  and an energy per bit  $eV_{op} \sim 10^{-20} J$ . The energy stored in the entire chip with 10<sup>12</sup> bits is only ~ 10 nJ.

In contrast to CMOS logic, single electron logic becomes more robust as the size of the devices decreases, and the operating temperature increases.

#### <u>Con</u> -

At present, very low temperatures (~1K) are required for operation. Extrapolating twenty years in the future, cooling to temperatures < 100K may still be required.

Operation at convenient temperatures ~ 100K requires device sizes < 10 nm well beyond the projected capability of CMOS foundries in 2010. New processing techniques to produce ultrasmall devices will be necessary.

Innovative processing techniques, such as those pursued by Hitachi, may lead to hysteretic memory based on single electron effects much sooner than 2010, if successful.

### Single Electron Memory and Logic Pro/Con (concluded)

The resistance of Coulomb blockade tunnel junctions must be much greater than  $h/e^2 = 24 \text{ k}\Omega$  in order to define a single electron charge. As a result, single electron devices have high characteristic impedance and are not well suited to driving transmission lines; additional conventional circuitry is required.

Stray charge, stray capacitance, and cotunneling are all problems, and their effects on large single electron circuits are not well understood at present.

### **Conclusions:**

### Superconducting and Single Electronics

# Conclusions

- CMOS technology will be viable for the next 20 years.

- But will it be the best (and most economical) technology?

- Revolutions may come through processing.

- The physical principles of rapid single flux quantum and single electron logic are sound.

- Rapid single flux quantum logic fast processors

- Single electron logic ultradense memory

- Serious disadvantages at present.

- Low temperatures required, low signal levels

- Future depends on processing and device development.

- Superconductivity high  $T_c$  transmission lines, high  $T_c$  SQUID's

- Single electron devices ultrasmall structures

### Conclusions

• CMOS technology will be viable for the next twenty years. We can expect continued improvements in performance, particularly through reductions in linewidth. However, the cost of fabrication facilities is already very high (~ \$500 million), and a tremendous investment will be needed to maintain exponential growth in capability. If the cost increases proportionately, continued exponential growth does not seem likely.

• Revolutions in performance (if they occur) are likely to come through advances in processing. The high cost of CMOS processing will provide a strong incentive to develop new methods of fabrication and alternative technologies.

• The physical principles of rapid single flux quantum (RSFQ) logic and single electron logic are sound, and the operation of small numbers of devices has been demonstrated. RSFQ logic is well suited to the construction of fast processors operating at very high clock rates ~ 10 GHz and greater. Single electron logic is particularly suited to the construction of ultradense single electron memory. Conversely, it appears difficult to make competitive memory with single flux quantum logic, or fast processors with single electron logic. Development of rapid single flux quantum logic can be pursued in the near future, because suitable fabrication technologies exist. Applications of single electron logic await suitable fabrication technologies and probably lie farther in the future.

#### Conclusions (Concluded)

• Both rapid single flux quantum logic and single electron logic possess serious disadvantages which will limit their application in the near future. The principal disadvantage at present is that low temperatures are required: T ~ 4K for RSFQ logic and T < 1K for single electron logic. RSFQ logic poses a number of problems generic to any high speed logic family: clock synchronization via self-timed logic, high speed memory organization, latency tolerance. These problems are more severe for RSFQ logic than CMOS logic because the speed is much higher. Single electron logic will require the development of new fabrication technology before operation at more convenient temperatures is possible. Both RSFQ and single electron logic are susceptible to relatively small stray magnetic (RSFQ) and electric (single electron) fields.

• The possible future use of rapid single flux quantum and single electron logic depend to a large extent on the development of new processing techniques and device technologies. The development of integrated high temperature superconductor transmission lines could be important both for cooled CMOS logic and for superconducting logic. The development of reliable high  $T_c$  superconductor SQUID's which can be made in quantity in integrated circuits would permit operation of RSFQ logic at more accessible temperatures ~ 80K and possibly above. The development of processing techniques to make ultrasmall structures for single electron logic could advance the time frame for ultradense single electron memory.

50

#### **Advanced Architecture**

This page intentionally left blank.

.

## **Advanced Architecture**

This study addresses high-performance computing in the year 2010 with particular attention to enabling technologies that should be developed in the next five to ten years to lay the groundwork for such machines.

There is a national need for "supercomputers", machines with performance that is five to ten years ahead of high-end desktop systems. These fast computers are needed to solve problems involving nuclear weapons, cryptanalysis, signal processing, and climate modelling. They also have applications in the commercial sector to do seismic analysis, simulate aircraft, automate product design and testing, and "mine" databases of information.

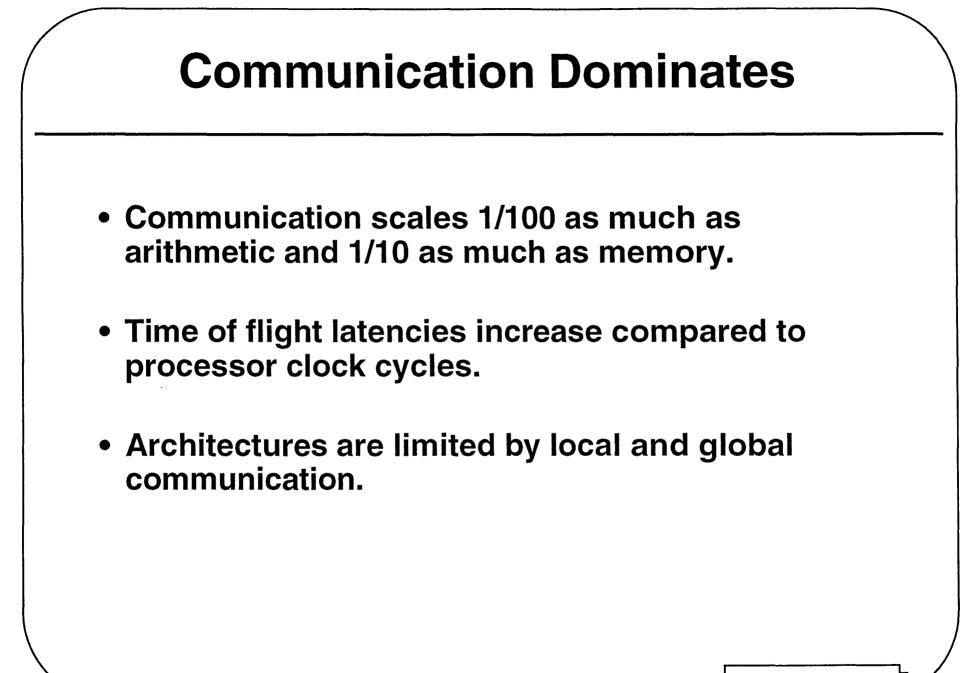

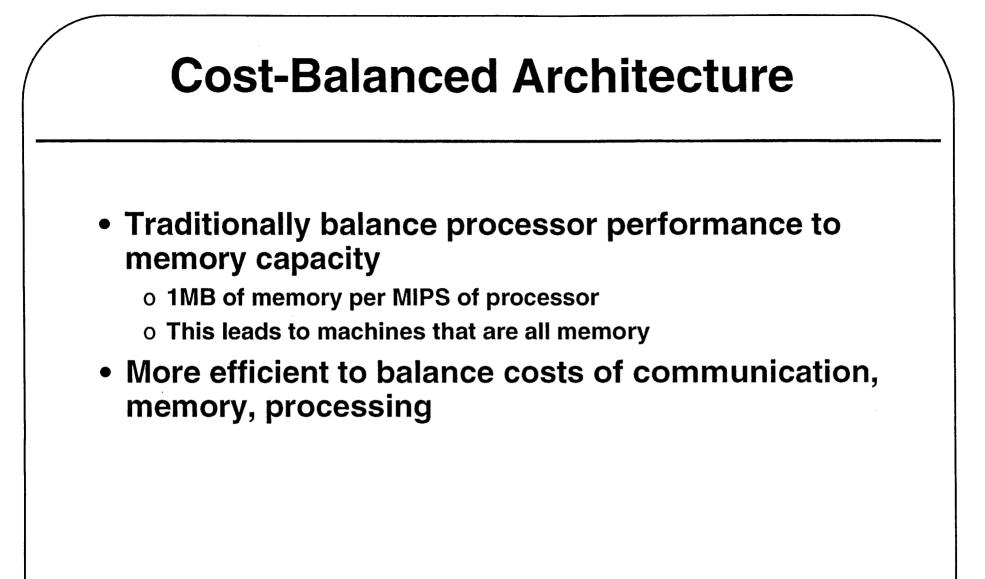

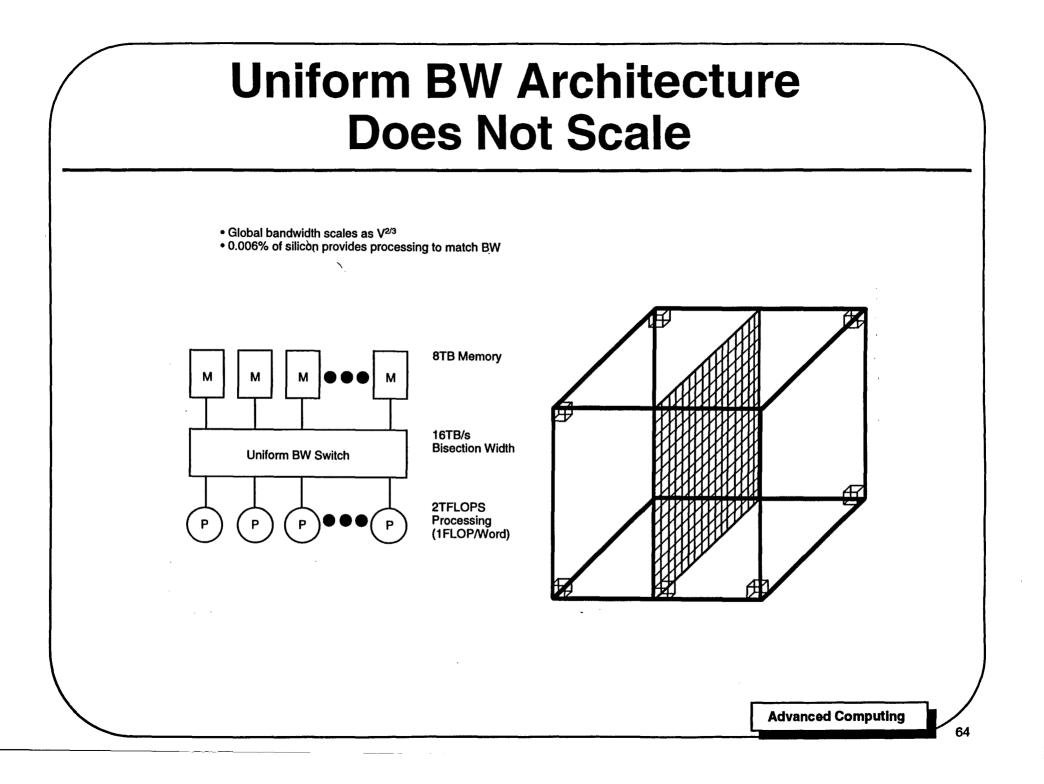

As computer technology changes, interconnection bandwidth is emerging as the limiting factor in the design of high-performance computer systems. The number of floating-point arithmetic operations per second (FLOPS) is becoming far less important than the number of bits per second of bandwidth between the processors, memories, and I/O devices in a system. A number of new hardware and software technologies are required to provide the maximum possible bandwidth and to use it most efficiently.